In a significant stride towards advancing quantum computing, researchers at Lawrence Berkeley National Laboratory have developed a groundbreaking technique to mitigate performance-reducing noise in chip substrates. This innovation is pivotal for boosting the capabilities of superconducting qubits, crucial elements in quantum computing.

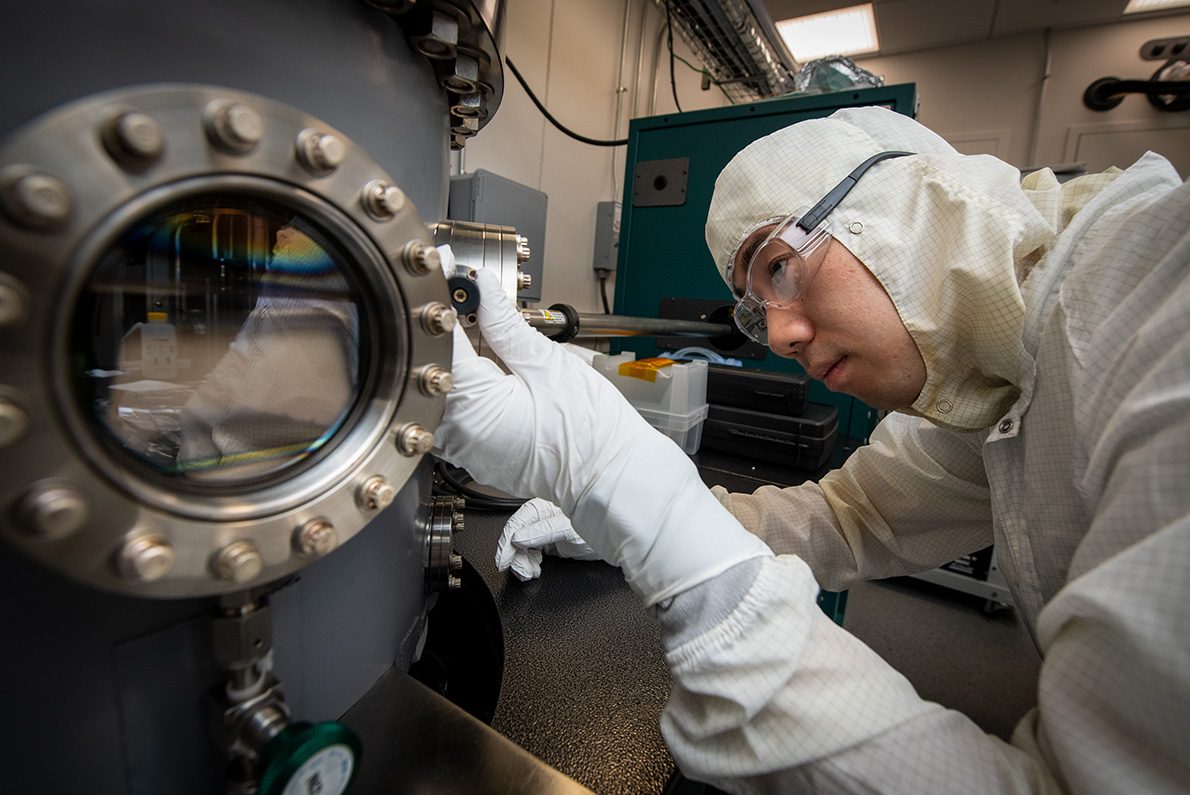

The team, including graduate student researcher Larry Chen, implemented a practical chemical etching process to elevate essential superconducting components called superinductors above the wafer surface. This novel suspension method minimizes physical contact, directly targeting stray capacitance and loss channels associated with the substrate. Their landmark research was featured in the journal *Applied Physics Letters*.

By integrating circuits such as resonators and qubits with these suspended superinductors—often utilizing Josephson junction arrays—the team achieved superior component quality. This strategy effectively curbs unwanted electrical interactions with the substrate, potentially reducing signal loss and enhancing component performance. Their approach offers a promising pathway toward developing quantum devices with robust resistance to environmental noise.

David I. Santiago, the study’s co-author and leader of the Quantum Information Science & Technology group at Berkeley Lab, highlighted the significance of this development: “Scientists worldwide have long aspired to reduce noise caused by defects in qubits—a complex challenge. Our simple chemical etching technique could be the missing link for anyone manufacturing superconducting microchips or qubit components.”

This advancement aligns with the Quantum Systems Accelerator (QSA) at Berkeley Lab’s mission to create manufacturable solutions for noise reduction. QSA director Bert de Jong emphasized the broader impact of this research, noting, “Developing noise-resistant qubits will propel us towards more efficient quantum computers, addressing key scientific challenges vital to the Department of Energy’s mission.”

Looking ahead, the Berkeley Lab team intends to apply this fabrication technique to directly construct qubits, integrating them into more intricate 3D architectures. The proposed etching framework is versatile, compatible with various superinductor types and planar circuit designs beyond the tested Josephson junction arrays. This adaptability promises scalable superconducting architectures with enhanced components, providing a foundation for investigating and mitigating fundamental loss mechanisms from device substrates. Ultimately, this could mark a crucial step toward realizing fault-tolerant quantum computers.

Source: https://www.rdworldonline.com/